# STM in the Small

Trading Generality for Performance in Software Transactional Memory

Aleksandar Dragojević<sup>1</sup> Tim Harris<sup>2</sup>

<sup>1</sup>I&C, EPFL Lausanne, Switzerland

<sup>2</sup>Microsoft Research Cambridge

presented by Thomas Herzog Concurrency and Memory Management Seminar Prof. Christoph Kirsch, University of Salzburg

Aleksandar Dragojević, Tim Harris STM in the Small

#### Motivation

- CAS vs STM

- Why STM is slow

- SpecTM

SpecTM

- Short Transactions

- Explicit Transactional Variables

- Combined Metadata with Value-Based Validation

# 3 Evaluation

- Skiplist

- Performance

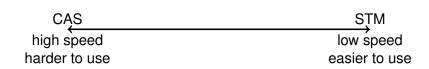

CAS vs STM

CAS vs STM Why STM is slow SpecTM

CAS vs STM Why STM is slow SpecTM

# Why STM is slow

- Book-keeping required when starting a transaction

- Taking a snapshot of processor state

- Managing the transaction record on each read and write

- Visiting meta-data locations for concurrency control

| Motivation | CAS vs STM      |

|------------|-----------------|

| SpecTM     | Why STM is slow |

| Evaluation | <b>SpecTM</b>   |

| Motivation |

|------------|

| SpecTM     |

| Evaluation |

CAS vs STM Why STM is slow SpecTM

- Provides a special API

- Improved performance

- Less generality

- Can be mixed with normal transactions

- Use normal transactions in the general case

- Use SpecTM API in performance-critical sections

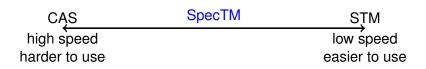

Figure 1: Throughput of operations on a hash table (90% lookups)

UNIVERSITÄT SALZBURG

Aleksandar Dragojević, Tim Harris STM in the Small

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validation

# **Traditional STM**

```

void *Items[OUEUE SIZE] = { NULL };

int LeftIdx = 0;

int RightIdx = 0;

void *PopLeft(void) {

void *result = NULL;

TX RECORD t;

do {

Tx Start(&t);

int li = Tx_Read(&t, &LeftIdx);

void *result = Tx_Read(&t, &Items[li]);

if (result != NULL) {

Tx_Write(&t, &(Items[li]), NULL);

Tx Write(&t, &LeftIdx, (li+1)%OUEUE SIZE);

}

} while (!Tx Commit(&t));

return result;

```

| Motivation |                                               |

|------------|-----------------------------------------------|

| SpecTM     | Explicit Transactional Variables              |

| Evaluation | Combined Metadata with Value-Based Validation |

# **Specializations**

- Short transactions

- Explicit transactional variables

- Combined metadata with value-based validation

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validat

# Short Transactions: Basic Idea

- Access only a small number of locations

- Indicate the sequence of operations

- Avoid write-to-read dependencies

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validati

## Short Transactions: Code Example

```

void *Items[OUEUE SIZE] = { NULL };

int LeftIdx = 0;

int RightIdx = 0;

void *PopLeft(void) {

void *result = NULL;

TX RECORD t;

restart:

int li = Tx RW R1(&t, &LeftIdx);

void *result = Tx_RW_R2(&t, &Items[li]);

if (!Tx_RW_2_Is_Valid(&t)) goto restart;

if (result != NULL) {

Tx_RW_2_Commit(&t, (li+1) % QUEUE_SIZE, NULL);

} else {

Tx RW 2 Abort(&t);

return result;

```

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validatio

## Short Transactions: Continued

- Each access must be to a distinct memory location

- Processor state is not saved

- Writes are deferred until commit-time

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

#### Short Transactions: API

#### typedef void \*Ptr;

// Single read/write/CAS transactions:

Ptr Tx\_Single\_Read(Ptr \*addr);

void Tx\_Single\_Write(Ptr \*addr, Ptr newVal);

Ptr Tx\_Single\_CAS(Ptr \*addr, Ptr oldVal, Ptr newVal);

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

## Short Transactions: API

```

// Read-write short transactions:

Ptr Tx_RW_R1(TX_RECORD *t, Ptr *addr_1);

Ptr Tx_RW_R2(TX_RECORD *t, Ptr *addr_2);

...

bool Tx_RW_1_Is_Valid(TX_RECORD *t);

bool Tx_RW_2_Is_Valid(TX_RECORD *t);

...

void Tx_RW_1_Commit(TX_RECORD *t, Ptr val1);

void Tx_RW_2_Commit(TX_RECORD *t, Ptr val_1, Ptr val_2);

...

void Tx_RW_1_Abort(TX_RECORD *t);

void Tx_RW_2_Abort(TX_RECORD *t);

```

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

### Short Transactions: API

```

// Read-only short transactions:

Ptr Tx_RO_R1(TX_RECORD *t, Ptr *addr_1);

Ptr Tx_RO_R2(TX_RECORD *t, Ptr *addr_2);

...

bool Tx_RO_1_Is_Valid(TX_RECORD *t);

bool Tx_RO_2_Is_Valid(TX_RECORD *t);

...

```

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

#### Short Transactions: API

// Commit combined read-only & read-write transactions: bool Tx\_RO\_1\_RW\_1\_Commit(TX\_RECORD \*t, Ptr val1); bool Tx\_RO\_1\_RW\_2\_Commit(TX\_RECORD \*t, Ptr val\_1, Ptr val\_2); ...

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

### Short Transactions: API

// Read-only short transactions: // Upgrade a location from RO to RW: bool Tx\_Upgrade\_RO\_1\_To\_RW\_2(TX\_RECORD \*t); ...

Short Transactions Explicit Transactional Variables Combined Metadata with Value-Based Validation

# Short Transactions: RO -> RW Upgrade

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validation

#### Short Transactions: Advantages

- No need for an update log

- Values written are provided at commit-time

- Read-after-write checks are no longer necessary

- Accessed locations can be held in a fixed-size inline array

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validati

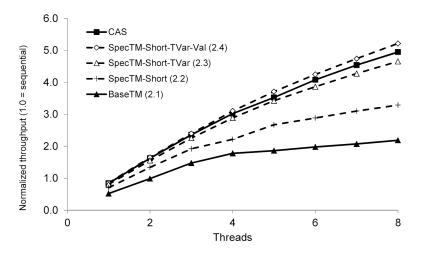

# Table of Ownership Records

Figure 2: Meta-data held in a table of ownership records, indexed by a hash function

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validation

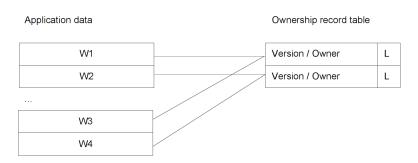

# **Explicit Transactional Variables**

| W1 | Version / Owner | L |

|----|-----------------|---|

|----|-----------------|---|

| W2 | Version / Owner | L |

|----|-----------------|---|

|----|-----------------|---|

| W3 | Version / Owner | L |

|----|-----------------|---|

|----|-----------------|---|

| W4 | Version / Owner | L |

|----|-----------------|---|

|----|-----------------|---|

Figure 3: Meta-data co-located with application data in TVars

S A L Z B U R G

Motivation

Short Transactions

SpecTM

Explicit Transactional Variables

Evaluation

Combined Metadata with Value-Based Validation

# Combined Metadata with Value-Based Validation

Figure 4: One lock-bit of meta-data held in each data item

# Value-Based Validation: Caution!

- Incorrect for the general case

- Special cases:

- Read-Modify-Write transactions lock orecs before update

- No version numbers needed

- Mostly-read-write transactions (one read-only location)

- RW locations are locked, RO location's value is compared

- Locations satisfy a "non-re-use" property

- The values are taking the place of version numbers

Skiplist Performance

- Uses short transactions for levels 1 and 2

- Uses normal transactions for higher levels

Skiplist Performance

■sequential ⊜orec-full-g Zorec-short-g Stvar-full-g ⊡val-full ©tvar-short-g □val-short

Figure 5: Single thread performance of SpecTM

Aleksandar Dragojević, Tim Harris STM in the Small

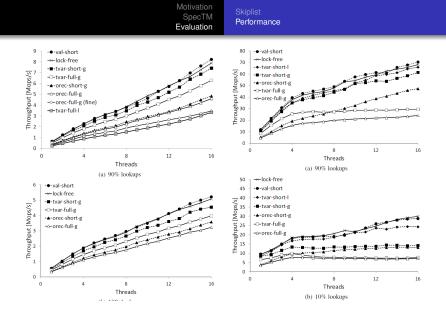

#### Figure 6: 16 cores

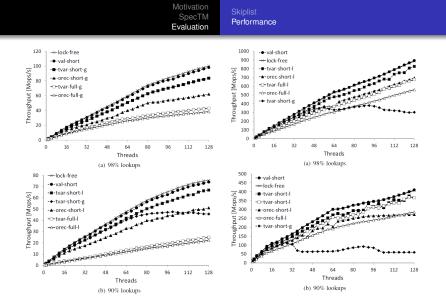

#### Figure 7: 128 Hardware Threads

## **References** I

# Aleksandar Dragojević, Tim Harris **STM in the Small**

Trading Generality for Performance in Software Transactional Memory

Proceedings of the 7th ACM european conference on Computer Systems (EuroSys '12). ACM, New York, NY, USA, 1–14., 2012.